- IC PAKCAGING THERMAL SIMULATION JOB DESCRIPTION HOW TO

- IC PAKCAGING THERMAL SIMULATION JOB DESCRIPTION SKIN

- IC PAKCAGING THERMAL SIMULATION JOB DESCRIPTION VERIFICATION

- IC PAKCAGING THERMAL SIMULATION JOB DESCRIPTION FREE

Note: Apple benefit, compensation and employee stock programs are subject to eligibility requirements and other terms of the applicable plan or program.Īpple is an equal opportunity employer that is committed to inclusion and diversity. Additionally, this role might be eligible for discretionary bonuses or commission payments as well as relocation.

IC PAKCAGING THERMAL SIMULATION JOB DESCRIPTION FREE

You’ll also receive benefits including: Comprehensive medical and dental coverage, retirement benefits, a range of discounted products and free services, and for formal education related to advancing your career at Apple, reimbursement for certain educational expenses - including tuition. Apple employees are eligible for discretionary restricted stock unit awards, and can purchase Apple stock at a discount if voluntarily participating in Apple’s Employee Stock Purchase Plan. The base pay range for this role is between $131,500 and $243,300, and your base pay will depend on your skills, qualifications, experience, and location.Īpple employees also have the opportunity to become an Apple shareholder through participation in Apple’s discretionary employee stock programs. This provides the opportunity to progress as you grow and develop within a role. At Apple, base pay is one part of our total compensation package and is determined within a range.

IC PAKCAGING THERMAL SIMULATION JOB DESCRIPTION HOW TO

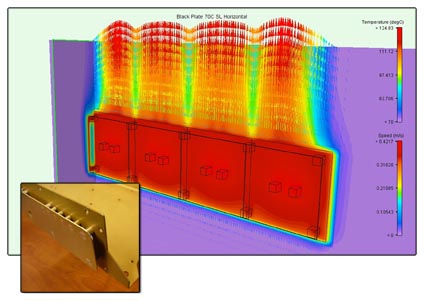

a AI or HPC processor without considering how to get the heat out is likely to lead to problems later on, resulting in a sub-optimal packaging solution from cost, size, weight and performance perspectives. Designing a large high power device, e.g. 2.5/3D IC package thermal modeling Modeling heterogeneous 2.5/3D IC-package thermal chip-package-interactions is important for several reasons. As an integral part of Xpedition Substrate Designer, it is immediately available to all package designers.

IC PAKCAGING THERMAL SIMULATION JOB DESCRIPTION SKIN

It is ideally suited for power integrity, low-frequency SSN/SSO, and complete-system SPICE model generation while accounting for skin effect impact on resistance and inductance. Full-3D electro-magnetic-quasi-static (EMQS) extractionįull package model creation with multi-processing for faster turnaround time. Calibre xACT provides accurate parasitic extraction of TSVs, front and backside metal, and TSV to RDL coupling. For a digital design, the designer must run static timing analysis (STA) on the complete package assembly, including parasitics. Intra-die & Inter-die parasitic extractionįor an analog design, the designer must simulate the system circuitry, including parasitics. Together, these automate SERDES channel analysis while retaining accuracy. These utilize automatic channel extraction, interface-level channel compliance verification, and pre-layout design exploration. Comprehensive SERDES analysis SERDES interface analysis and optimization include FastEye diagram analysis, S-parameter simulation, and BER prediction.

IC PAKCAGING THERMAL SIMULATION JOB DESCRIPTION VERIFICATION

From pre-route design exploration and “what-if” analysis through detailed verification and sign-off, all with fast, interactive analysis, ease-of-use, and integration with Package Designer. Analyze s ignal integrity (SI) issues in the design cycle HyperLynx SI supports general-purpose SI, DDR interface signal integrity and timing analysis, power-aware analysis, and compliance analysis for popular SerDes protocols. Results can be reviewed in graphical and report formats. Identify potential DC power delivery issues such as excessive voltage drop, high current densities, excessive via currents and associated temperature rise including co-simulation for signal/power/thermal impact. Power distribution networks can be analyzed for voltage drop and switching noise issues. Analysis of voltage drop & IC switching noises

0 kommentar(er)

0 kommentar(er)